Description

A pair project where we had to investigate and implement an increasingly complicated hardware / software implementation of a math function on an FPGA for an Intel NIOS II processor.

Details

| Skills: | FPGA Hardware Optimisation System Verilog |

| Scope: | University |

| Date: | March 2023 |

Responsibilities

My responsibilities for this project mainly included creating logical designs for the necessary hardware blocks, testing them and writing about them in the report.

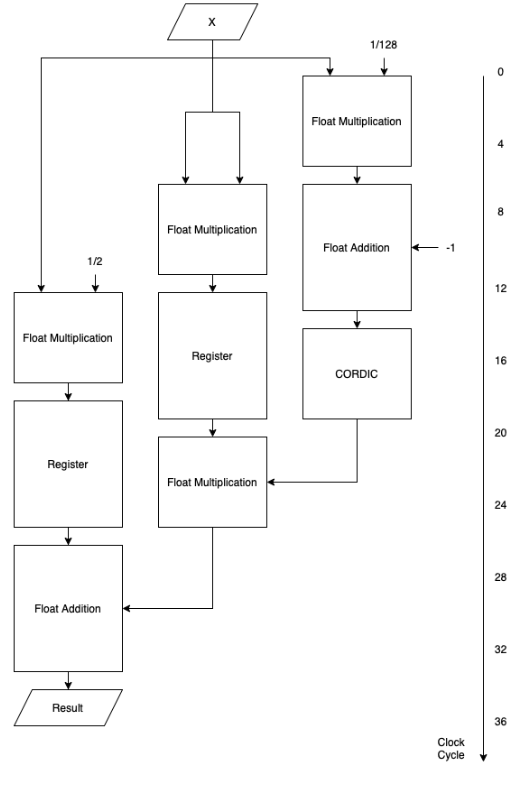

- Implemented Fixed Point to Floating Point (and vice versa) conversion blocks, capable of conversion within a single cycle.

-

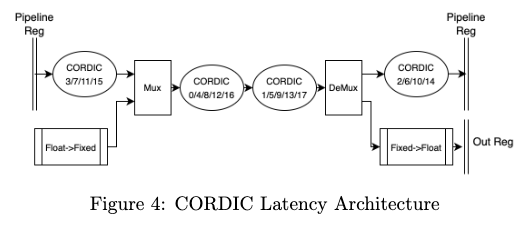

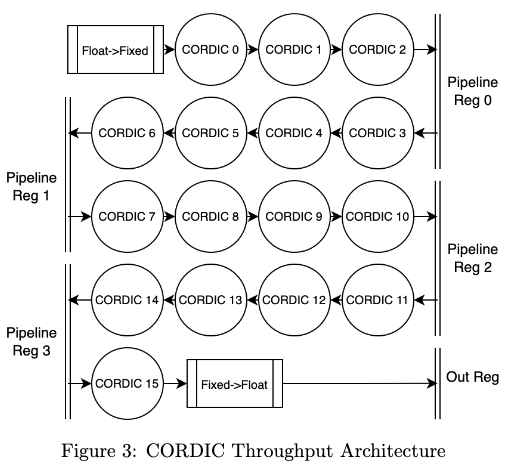

Designed and Tested a multi-stage CORDIC block for the calculation of Cosines.

- Designed a CORDIC Architecture in C++ using OOP principles with configurations for the number of stages and the number of bits.

- Investigated the effects of the configurations on the MSE and Confidence Interval using Python, finding the optimal values of these parameters for the requirement of a maximum MSE of 10-10 and a confidence interval of 95%.

- Converted the C++ design into System Verilog and added it as a hardware acceleration unit on the FPGA.

- Implemented Hardware Floating Point Addition/Subtraction/Multiplication blocks. These were not used since complete implementations were provided for the project.